Well, here we are at the end of 2024. Already.

I get a lot of questions along the lines of “where are we at”, “why is it taking so long” etc etc…

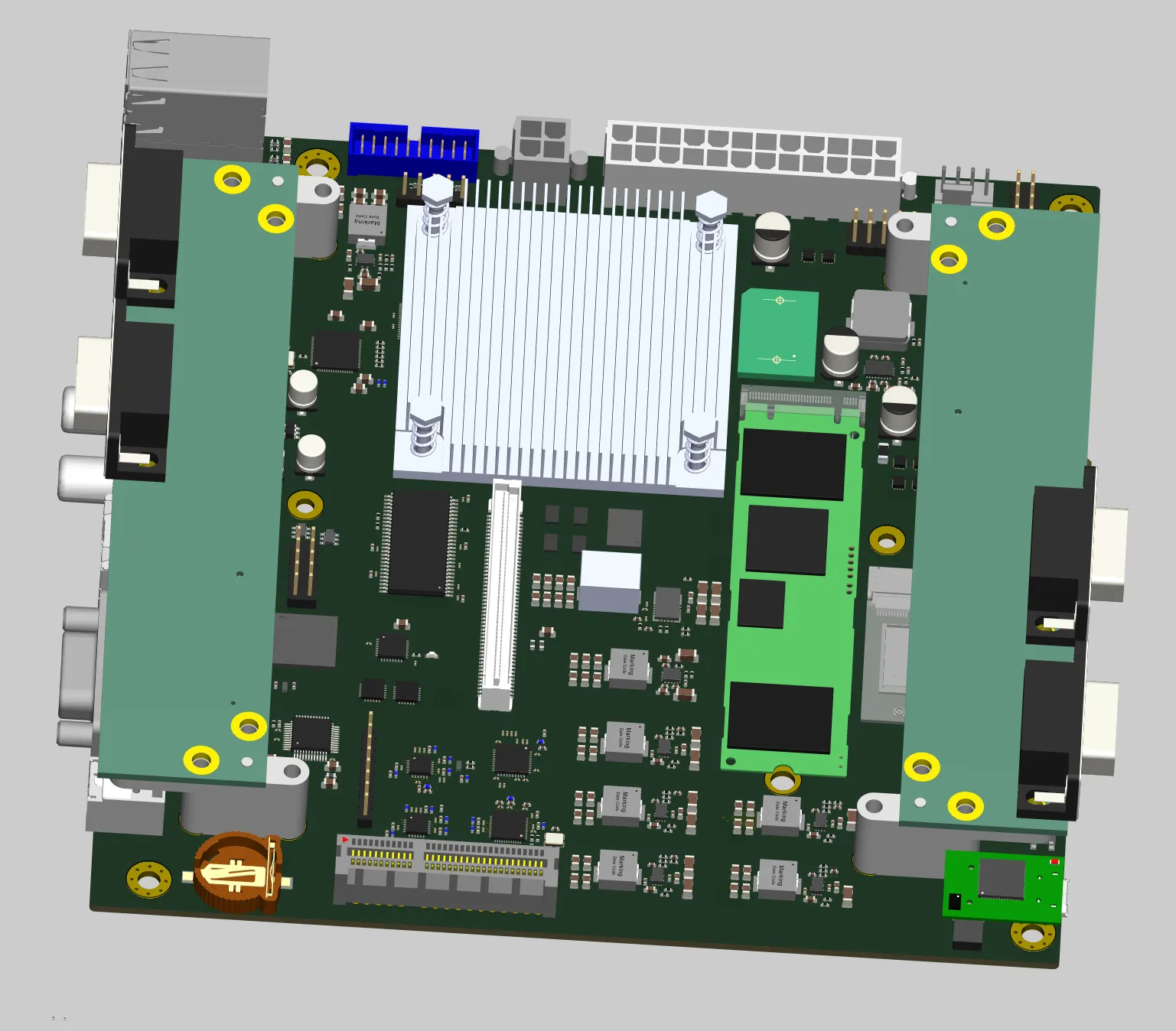

Replay2 is a complex board both electrically and mechanically. I am trying to do it at a low cost, which means a low layer count PCB. The design drawing (schematic)...

Categories

- core-updates (15)

- general (121)

Blog: All Posts

I’m not doing very well at posting updates here, the Discord is where to be to get the latest gossip as we struggle to complete the design. The link below will work for a week, I’ll post another update after that.

https://discord.gg/UFHPxsMc

We are out of NDA with Intel now and the Agilex5 info is publicaly available – as is the tool...

It’s been an exciting two months learning about the new Intel Agilex5 and the RK3588 used in our new Replay2 platform. The design and schematic are nearly completed – after a number of last minute changes/improvements.

Samples of the part are on the way and we’ll post some detailed layout images and specs of the board in the near future.

I’m also...

It's been a long time coming, but we are really excited to announce that Replay2 will be based around the Intel Agilex5 FPGA...

It's been a long time coming, but the desk is clean and ready for the first hardware prototype, hopefully December '23.......

Good things come to those who wait...

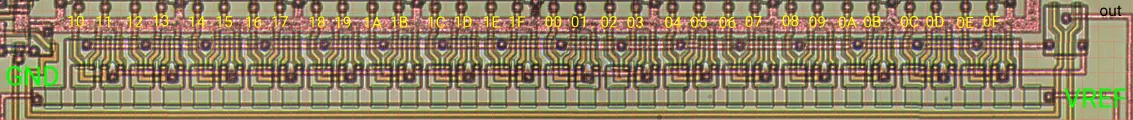

I'm fully focused on Replay2 currently, but just a quick update on the Namco CUS34 replacement. I really wanted to complete the alternative mode used on ToyPop and Libble Rabble.

Using my 20 year old bit of vero-board, I can compare the replacement and real chip directly. The logic analyzer connects to both parts and dip switches let me isolate outputs...

I've been shipping Namco CUS34 replacements for a while and the majority of the engineering work was done over 10 years ago. Reverse engineering the silicon by decapsulation of the die, taking pictures and manually tracing them is best way to understand what is going on, but it's very time consuming. Most of these chips are quite simple and have...

The investigations up to this point remained entirely in the digital domain. Waveforms like the ones shown in the post were derived from the PCM data right before it enters the DAC. This is most suitable to obtain precise information about the cycle behaviour of the design but neglects the final conversion step from digital to the analog output...

- « Newer

- 1 / 17

- Older »