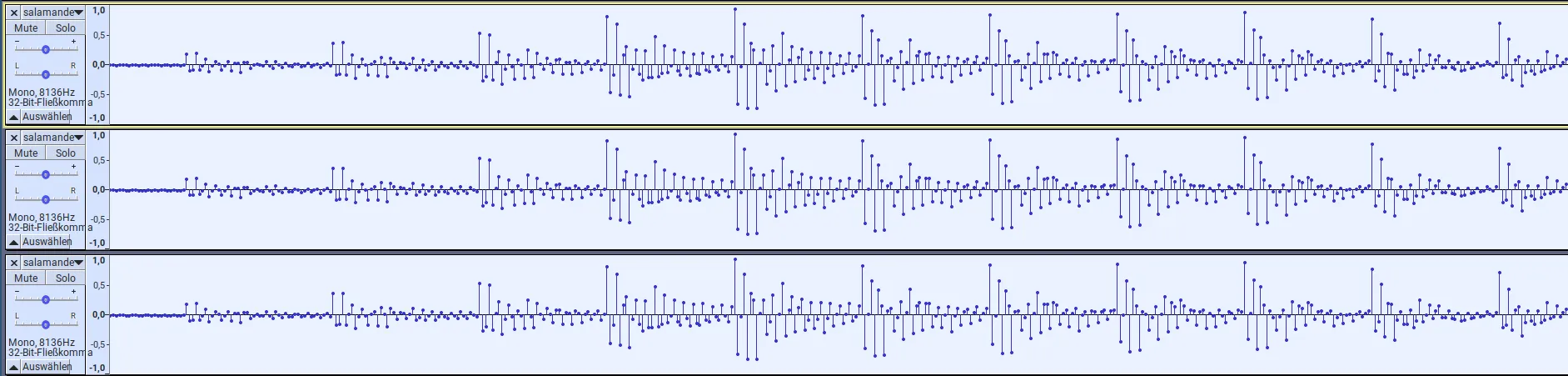

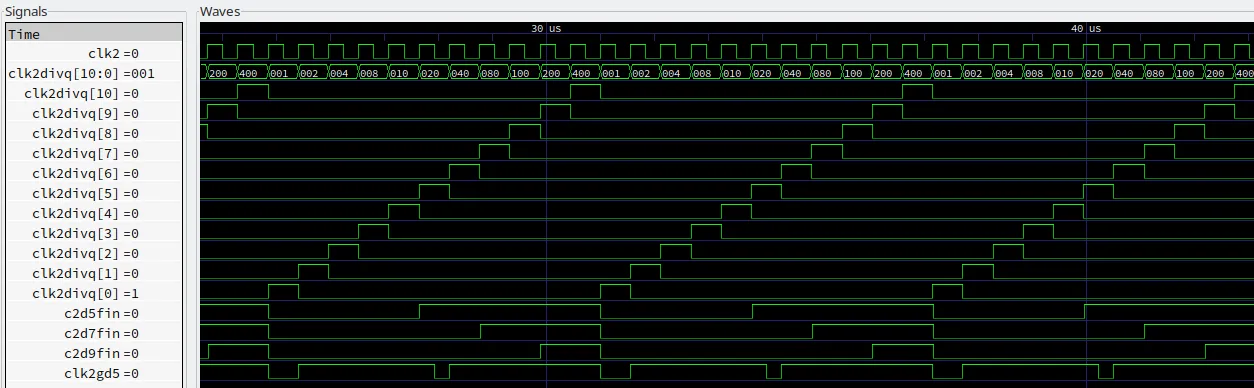

The investigations up to this point remained entirely in the digital domain. Waveforms like the ones shown in the post were derived from the PCM data right before it enters the DAC. This is most suitable to obtain precise information about the cycle behaviour of the design but neglects the final conversion step from digital to the analog output...

Categories

- core-updates (15)

- general (121)

Blog: core-updates

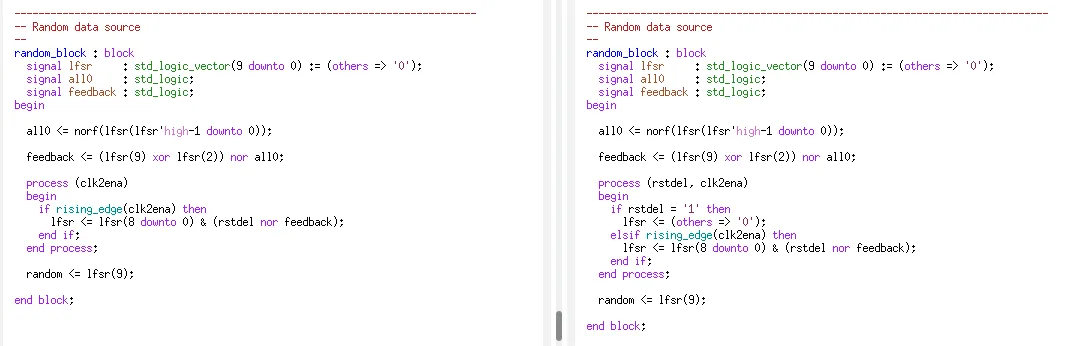

What could cause that the for certain frames? The usual suspects are incomplete reset and ...randomness. Lots of internal states / flip-flops aren't affected by the RST input, so that could be a cause for repeated execution of the same speech sample. The random source is not strictly random, however. It's an LFSR and as such it has a...

Now with the in place, how does it perform?

The initial validation consisted of two basic phases:

VHDL simulation in a test bench that dumps the PCM audio to a binary file. The binary is imported with Audacity and converted to WAV format for listening. Goal: Prove that the design can actually generate correct samples in a flexible environment.

Integration of the...

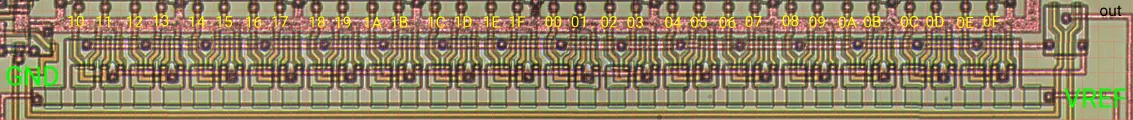

When I started to search for the the first challenge was the decision where to begin with. Looking at the , there are not many landmarks that provide clear guidance. The ROMs are quite prominent due to their regular structure, but they don't have a direct relationship to the random generator. Furthermore, the purpose of two of the three...

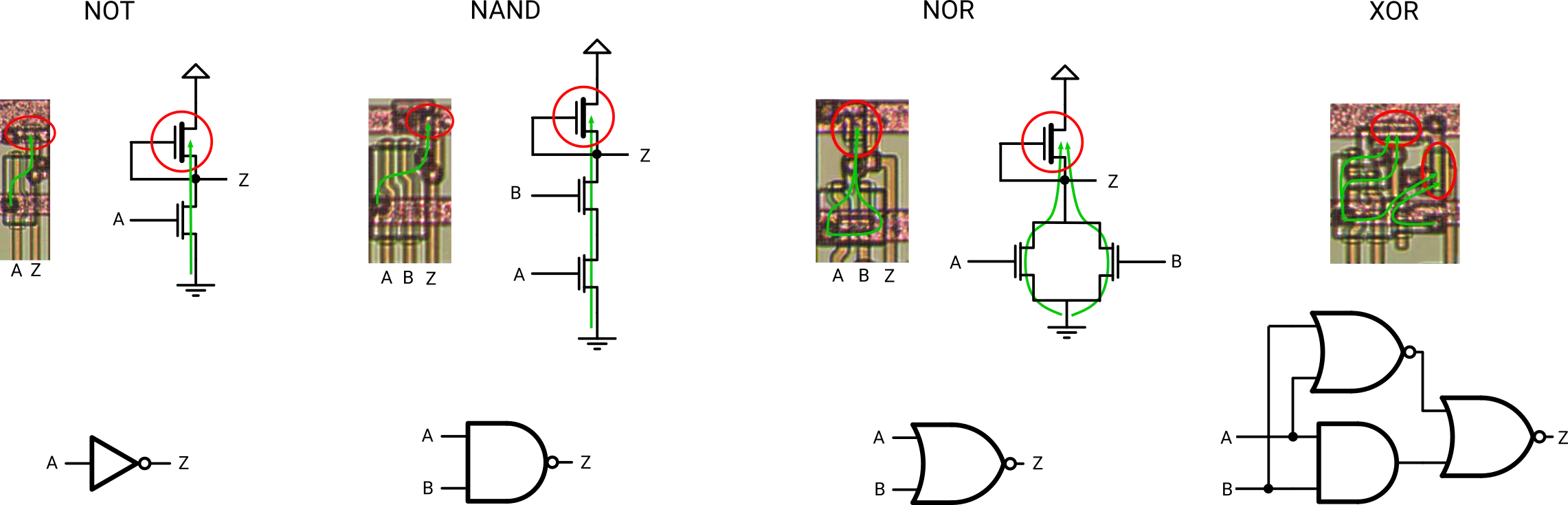

We need to set the stage first for this post. The is built from . This means there are basically two types of devices:

Enhancement-mode NMOS transistors for shorting a node to GND (or forwarding voltage between two nodes)

Depletion-mode NMOS transistors to act as pull-ups to VDD

In addition, there are a total of three layers to connect devices in decreasing...

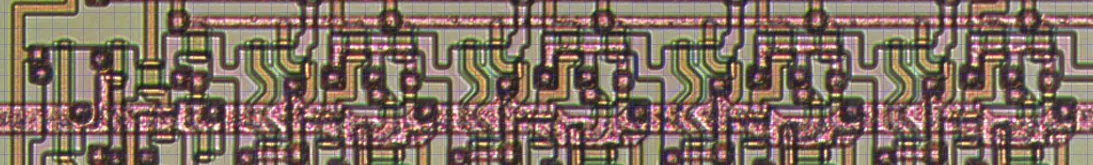

The introduced a tracing procedure to extract logic gates from VLM5030's layout information. This post shows how the procedure can be extended to extract VLM5030's embedded ROMs.

The image below shows a portion of the sequencer ROM:

The blue metal bar is GND

The horizontal red metal bar is bitline 0 (out of 37)

The vertical orange polysilicon wires represent a total of...

Quite a couple of Konami cores use the chip to generate human-like speech for in-game effects. While the replacement design created for the replay library does its job, it still falls behind the audio of an original chip. This is mainly due to the fact that the design was built based on without detailed information of the chip's...

There has been quite a lot of work going on in the background with the FPGA Arcade project, not the least of which is a host of new core releases.

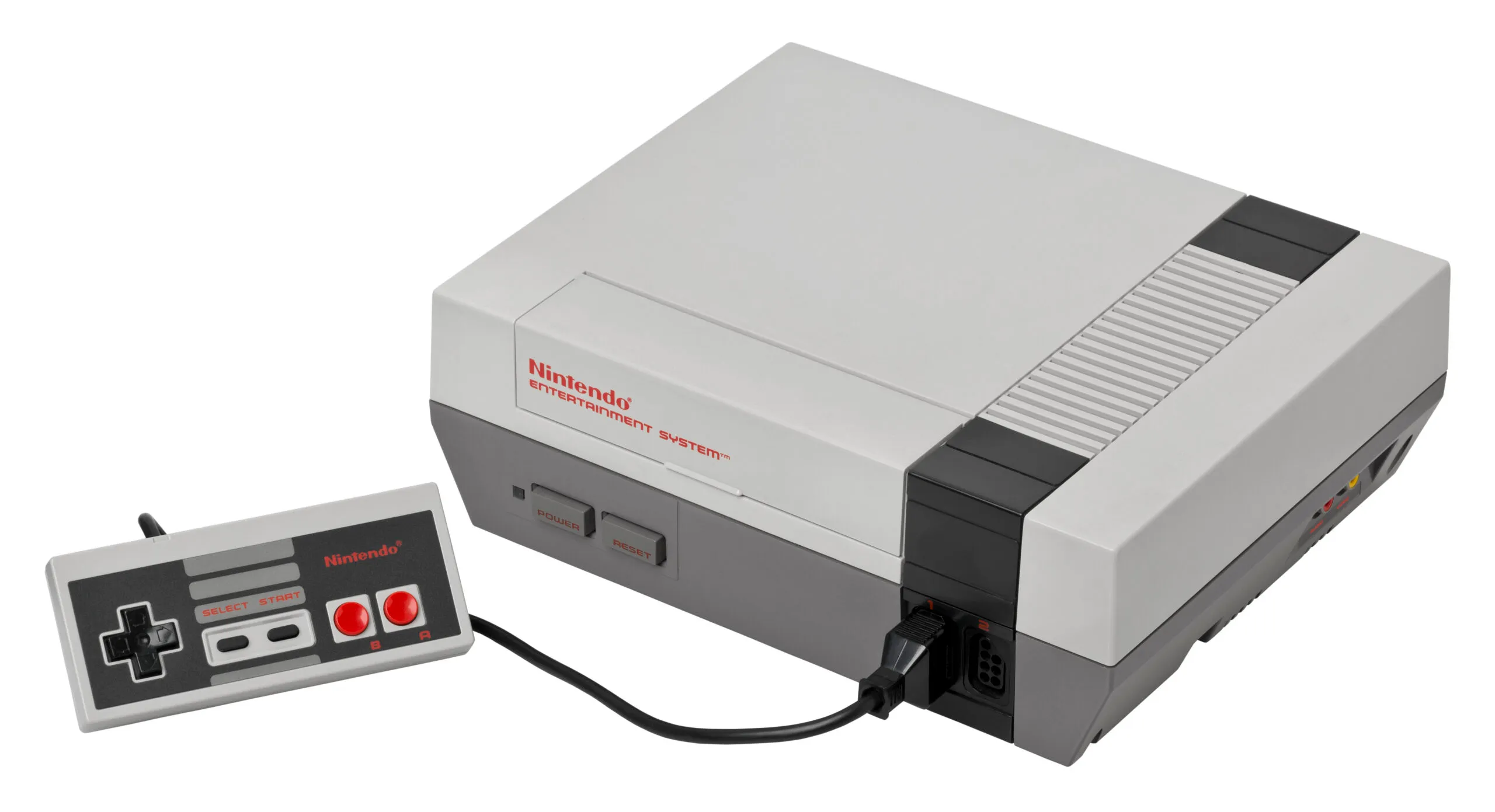

As you may have guessed from the image, the NES is now available for the Replay and MKR Vidor4000 platforms. This version of the NES core includes a transistor net-list based...

- « Newer

- 1 / 2

- Older »